4DSP Compact Embedded System Performance Boosted by UltraScale and SDAccel

We recently announced two new additions to our innovative compact embedded system (CES) product line. The CES820 and ruggedized CESCC820 both benefit from powerful new Kintex UltraScale FPGAs supplied by longtime 4DSP partner Xilinx, and they offer support for the most recent version of Xilinx’s SDAccel development environment for OpenCL™, C, and C++. While the CES820 features the same durable aluminum enclosure as the CES720, which 4DSP introduced in 2014 to much enthusiasm from our customers, it represents a step forward in performance for the CES line.

We recently announced two new additions to our innovative compact embedded system (CES) product line. The CES820 and ruggedized CESCC820 both benefit from powerful new Kintex UltraScale FPGAs supplied by longtime 4DSP partner Xilinx, and they offer support for the most recent version of Xilinx’s SDAccel development environment for OpenCL™, C, and C++. While the CES820 features the same durable aluminum enclosure as the CES720, which 4DSP introduced in 2014 to much enthusiasm from our customers, it represents a step forward in performance for the CES line.

The CESCC820 goes even further by providing a conduction-cooled and more vibration-resistant chassis, as well as military-grade Meritec connectivity options. The more spacious, yet still compact enclosure offers the choice to install more than one FPGA Mezzanine card (FMC) inside as a build option. These attributes make the ruggedized model an ideal choice for a wide range of deployed embedded aerospace and defense applications where Size, Weight, and Power (SWaP) are critical and more demanding IO or DSP requirements are called for.

Both CES820 versions have a quad-core, low-power Intel Atom CPU that is tightly coupled to the FPGA, making them perfect for handling the high-level programmability necessary to perform anti-jamming, compression, encryption, high-performance signal processing for such applications as communication signal analysis. The full list of features, data sheets, block diagrams, and additional photos of these systems can be found on their respective product pages: CES820 and CESCC820.

Both CES820 versions have a quad-core, low-power Intel Atom CPU that is tightly coupled to the FPGA, making them perfect for handling the high-level programmability necessary to perform anti-jamming, compression, encryption, high-performance signal processing for such applications as communication signal analysis. The full list of features, data sheets, block diagrams, and additional photos of these systems can be found on their respective product pages: CES820 and CESCC820.

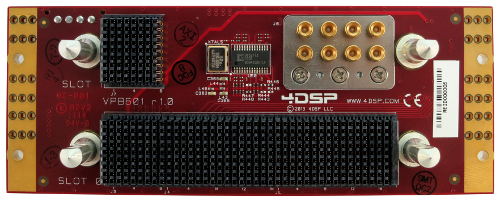

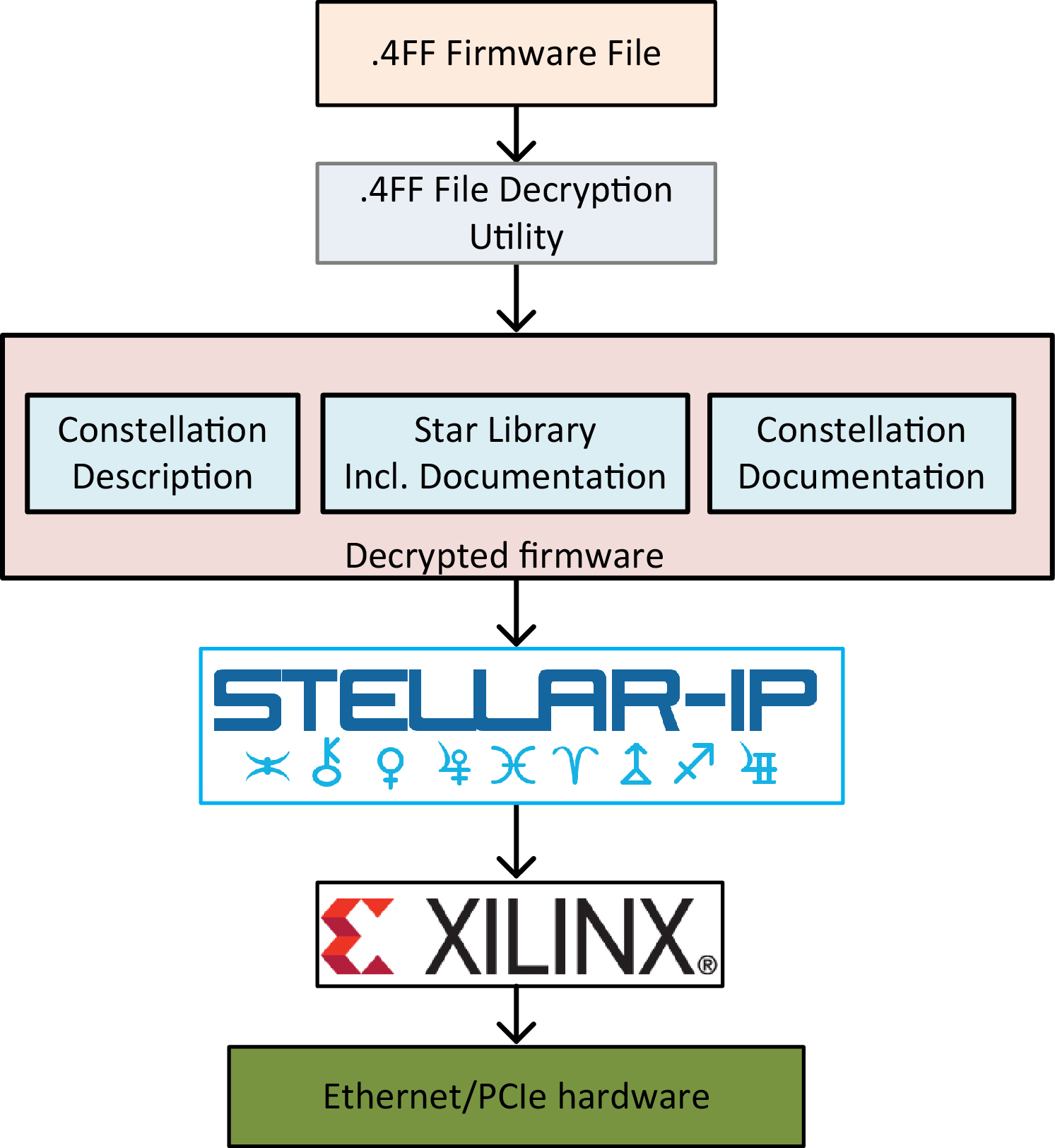

FMC modules for these systems can be selected from 4DSP’s extensive and diverse portfolio or from a third-party vendor enabling extensive functional customization using VITA 57.1-compatible FPGA mezzanine cards. The 4DSP Board Support Package (BSP) and StellarIP firmware tool and library are included with these systems. These intuitive tools allow designers to jump into development with modular reference designs that exercise the systems’ capabilities and provide high-level interfaces and driver support.

These systems support the Xilinx SDAccel FPGA development environment. The newest version of SDAccel (2015.1) offers enhancements that make the Eclipse-based integrated development environment easier to use as a result of new debug and profiling features that speed the development and deployment of OpenCL, C, and C++ kernels. This release also builds on SDAccel’s Khronos standard compliance, supporting a new OpenCL Installable Client Driver (ICD). The ICD extension allows multiple implementations of OpenCL to co-exist on the same system, giving applications developers the ability to choose between CPUs, GPUs and FPGAs in real-time. This accelerates run time and results in power savings.

Looking ahead, as an SDAccel development environment-certified Xilinx Alliance Member, 4DSP’s future FPGA-based board and system-level products will also support SDAccel as part of our continuing effort to give system designers the very best tools for efficiently achieving great results.

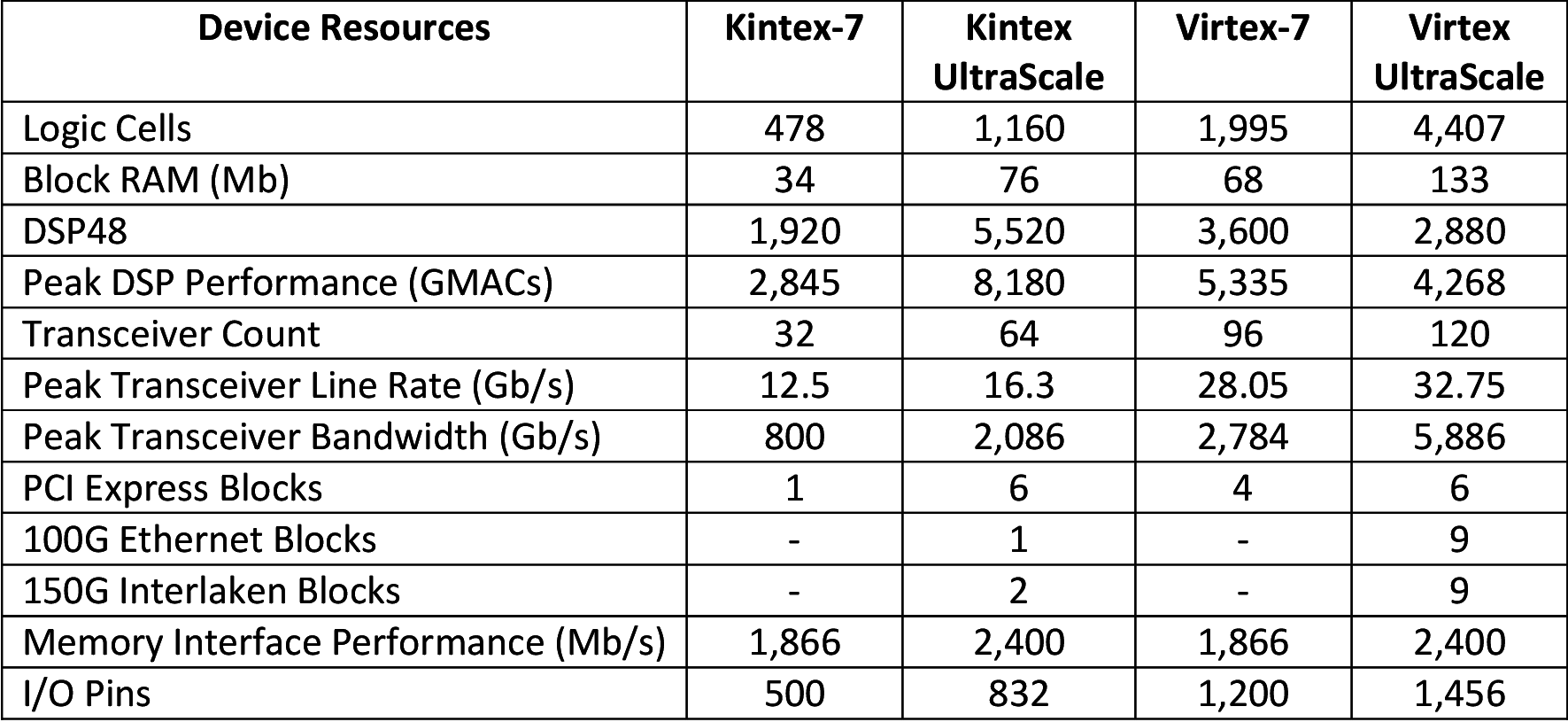

eneration of Xilinx FPGAs in its most recent products. The basic logic cell structure of these

eneration of Xilinx FPGAs in its most recent products. The basic logic cell structure of these

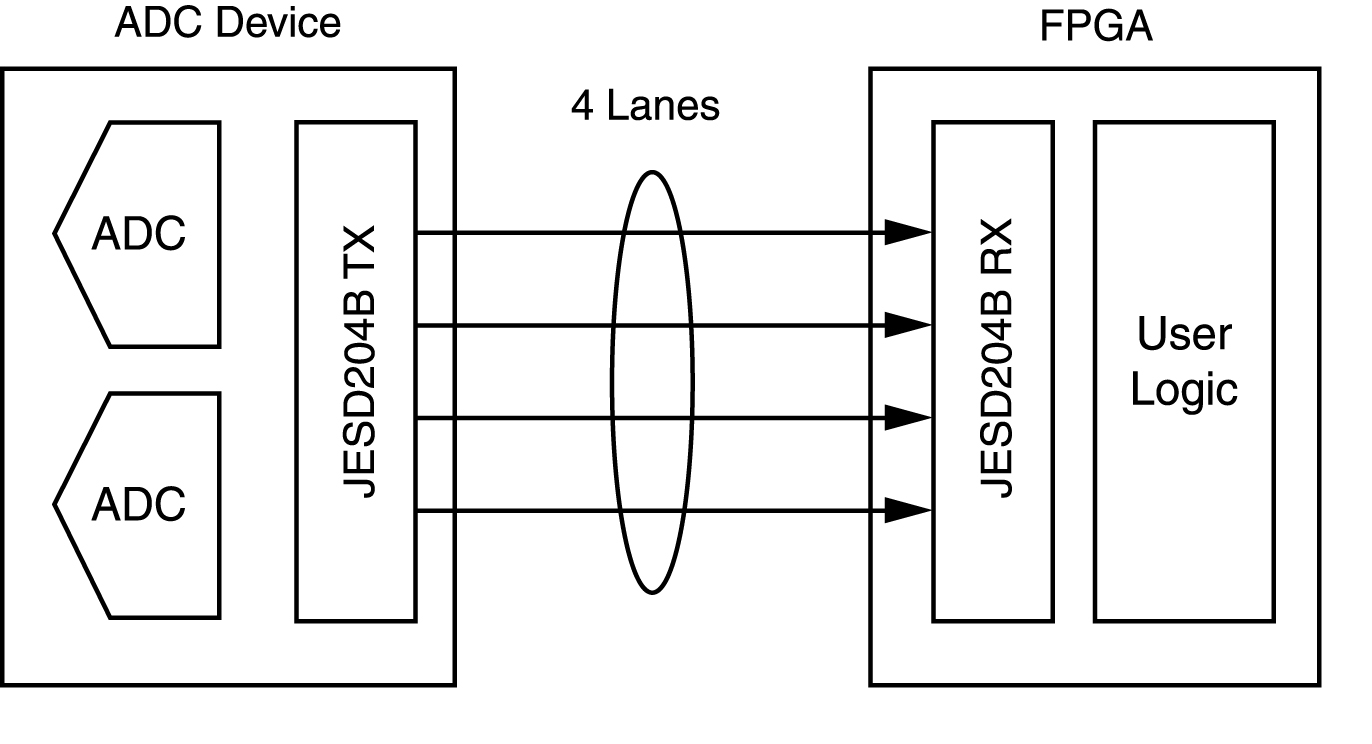

4DSP Firmware compilation chain

4DSP Firmware compilation chain