New 4DSP White Paper Roundup

4DSP has added a few new white papers to our website to provide more information about some of our products and elaborate on the functional advantages of the technologies and standards they are based upon. We also highlight some of the challenges inherent to several applications and demonstrate how our boards, backplanes and systems can help you achieve a successful design while minimizing both costs and development times.

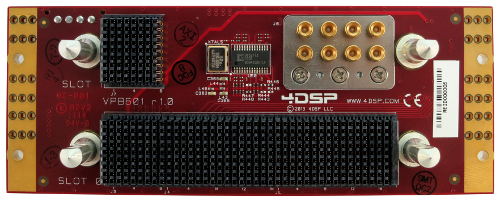

The product page for our compact and highly adaptable line of FlexVPX 3U VPX-compliant backplanes now features a paper outlining the benefits of this innovative design for VPX systems and some context about the growth of the OpenVPX (VITA 65) standard for systems development. The paper features a contribution from the US Naval Research Laboratory, where the FlexVPX concept was developed as a way to reduce the Size, Weight and Power (SWaP) of embedded systems using two and three-slot backplanes that allow for backplane functionality to be subdivided across several smaller boards. This increases flexibility in the physical packaging of system processing hardware to accommodate the limited physical space available in many military and commercial systems.

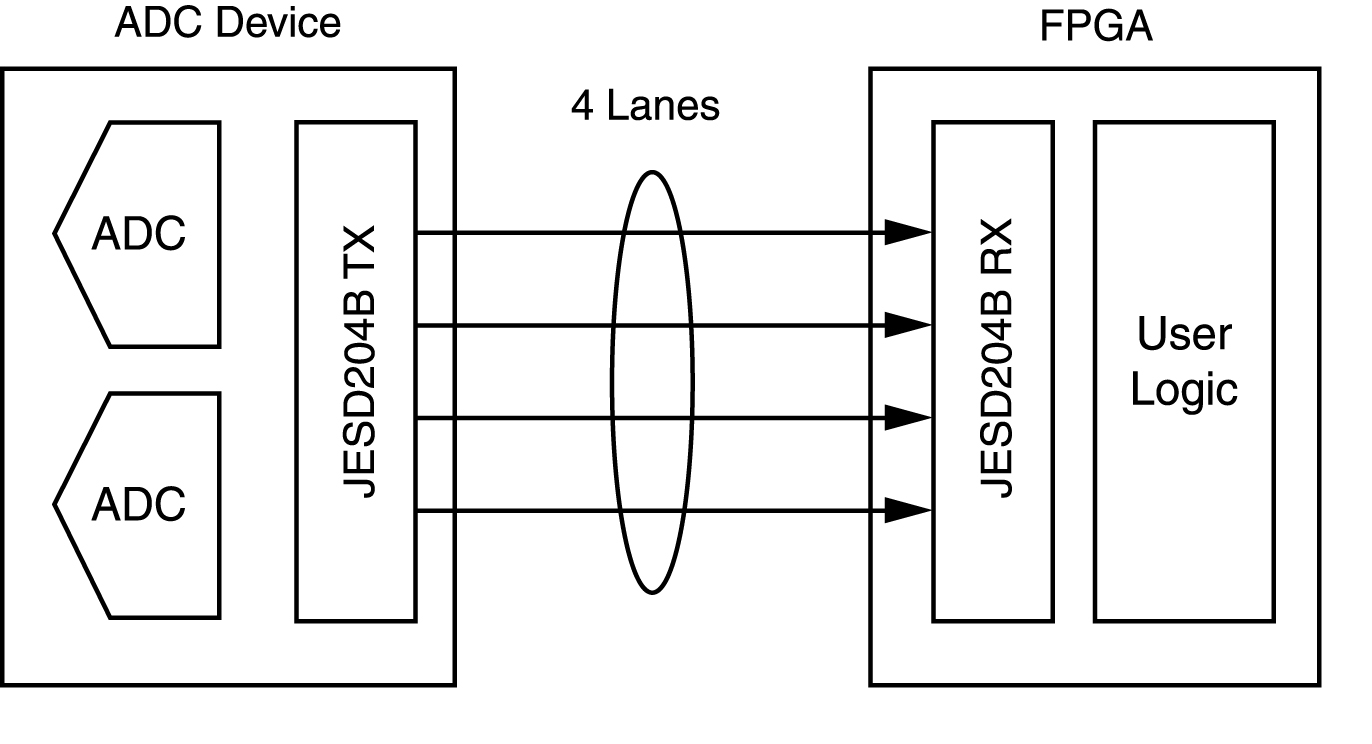

To support our FMCs (FPGA mezzanine cards) that make use of the JESD204B serial interface standard, another white paper is available on the product pages for the FMC144, FMC142, FMC140, and FMC176 modules. JESD204B offers a reliable, efficient and flexible alternative to the typical LVDS and CMOS interfaces used between FPGA or DSPs and data converters. It reduces the number of interconnects required to interface high-speed (>10 Msps) ADC and DAC converters on an FMC to an FPGA on a carrier card. This makes it possible to design for smaller form factors while maintaining system performance.

Typical ADC to FPGA Configuration Using JESD204B (source: Xilinx)

Multi-antenna array (photo Gareth Ellner)

We look at the topic of using FPGAs for beamforming in wireless telecommunications and radar applications in the FPGAs for Better Beamforming Performance paper featured on many of the pages for products that are well suited for beamforming, including the Xilinx Virtex-7-based FM788 and the FMC168.

The heavy computational loads and very high bandwidth required to digitally process signals in real time can quickly overtax traditional CPUs and DSPs when used in adaptive beamforming for mobile networks. Much higher performance FPGAs, on the other hand, are ideal for this purpose due to their embedded DSP blocks, parallel processing architecture, and enhanced memory capabilities. FPGAs similarly offer a big advantage over CPU and GPU options in radar systems that employ advanced digital beamforming techniques because they can reduce, cost, complexity, and power consumption.

The VPX for System Development white paper looks at the cost benefits of using the VPX standard (VITA 46) when designing high-performance, rugged embedded systems for aerospace and defense applications involving high-frequency signals. It is available on the product pages for our 3U VPX FPGA carrier cards, such as the VP780, and our VPX systems, including the VPX360.

The paper outlines the advantages of using designs centered on FPGAs and FMCs to improve project risk management and reduce time-to-market. The OpenVPX ecosystem offers flexibility and performance when planning new designs. It is effective for system upgrades and technology insertion, and it simplifies the incorporation of new technologies such as higher resolution A/Ds and D/As as they become available.

More white papers are in the works on other topics and technologies, so stay tuned!