# Tutorial StellarIP Interface To AXI Interface

4DSP LLC

Email: support@4dsp.com

This document is the property of 4DSP LLC and may not be copied nor communicated to a third party without the written permission of 4DSP LLC.

© 4DSP LLC 2014

# **Revision History**

| Date       | Revision        | Revision |

|------------|-----------------|----------|

| 2014-07-18 | Initial release | 1.0      |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

|            |                 |          |

## **Table of Contents**

| 1 | Intr | oduction                             |

|---|------|--------------------------------------|

|   | 1.1  | Overview                             |

|   | 1.2  | Requirements                         |

|   | 1.3  | Terms and definitions                |

| 2 | Obt  | aining 4DSP IP Source Code5          |

|   | 2.1  | Locate the VHDL source code          |

|   | 2.2  | Copy the required IP source files    |

| 3 | Cor  | version entities                     |

|   | 3.1  | Wormhole Output to AXI-Stream Master |

|   | 3.2  | Wormhole Input to AXI-Stream Slave   |

|   | 3.3  | StellarIP Command to AXI-Lite        |

| 4 | Wra  | apping into AXI 10                   |

| 5 | Sim  | ulate                                |

|   | 5.1  | File descriptions                    |

|   | 5.2  | Creating the project                 |

|   | 5.3  | Creating the test bench              |

|   | 5.4  | Running Simulation                   |

|   | 5.4. | 1 Command Interface                  |

|   | 5.4. | 2 ADC and DAC Interfaces             |

| 6 | Syn  | thesize                              |

|   | 6.1  | File Descriptions                    |

|   | File | or Folder                            |

|   | 6.2  | Modifying the project for synthesis  |

|   | 6.3  | Creating the top level               |

|   | 6.4  | Running and Initialization           |

|   | 6.4. | 1 Initialization Script              |

|   | 6.5  | Capturing ADC Data                   |

|   | 6.6  | DAC Results                          |

| 7 | Ref  | erences                              |

# **1** Introduction

StellarIP is a block-based IP integration solution similar to Xilinx Vivado IP Integrator. One important difference is that StellarIP blocks generally do not use AXI Interfaces. Since the StellarIP Catalog has fully functional IP for all 4DSP Hardware including host interfaces, memory controllers, and FMC Board Controllers, there might be a desire to reuse this code within a system using AXI Interfaces. This document is meant to be a guided description on how to convert a typical StellarIP block to have an AXI Interface.

To make this guide concrete the FMC110 IP Block (sip\_fmc110) will be used, but the techniques can be applied to any StellarIP Block. The FMC110 IP Block is an Interface Controller for a 4DSP FMC110 daughter card which is a dual channel 12-bit ADC and a dual channel 16-bit DAC. The FMC110 controller is able to configure the clock tree, ADCs and DACs as well as capture data from the ADC and send data to the DAC.

### 1.1 Overview

To convert the FMC110 IP Block to AXI we first obtain the source code and create an AXI wrapper around it. At this point the interface conversion is complete but we continue with a simulation to gain confidence and finally build a design targeting a Xilinx VC707 development board to prove functionality.

## **1.2 Requirements**

The following tools are required to completely follow this tutorial:

- 4DSP FMC110 Daughter Card

- Xilinx VC707 Carrier Board

- 4DSP Board Support Package

- Xilinx Vivado 2014.1 or later

- Python Programming Language Interpreter

- Analog Devices VisualAnalog

Please refer to the Xilinx user guides, 4FM Getting Started Guide, and other 4DSP documents to make sure all of these are properly installed.

## 1.3 Terms and definitions

Throughout the document the following terms are used with the indicated definitions

| Entity                  | A VHDL keyword to define an interface. More abstractly it can represent a   |  |

|-------------------------|-----------------------------------------------------------------------------|--|

|                         | functional block or an actual file with VHDL code.                          |  |

| StellarIP Block or Star | All source code that makes up a StellarIP Block. A top level entity and all |  |

|                         | sub-entities.                                                               |  |

| Interface or Channel    | A collection of signals.                                                    |  |

# 2 Obtaining 4DSP IP Source Code

All 4DSP Hardware comes with a Board Support Package that includes an FPGA reference design that that exercises the functionality of the hardware. Since in this tutorial we want to take the FMC110 StellarIP Block and convert it to have an AXI-Interface we first need to obtain all the source code we are going to reuse.

#### 2.1 Locate the VHDL source code.

It is typically located in the star lib folder "/star\_lib/sip\_fmc110".

#### 2.2 Copy the required IP source files.

The FMC110 IP is designed to work with many different carrier boards having different FPGAs so there might be different version of files that are used with different FPGAs. To know which files are needed a list is provided depending on what FPGA is being used.

|  | Table | 1: | Source | List |

|--|-------|----|--------|------|

|--|-------|----|--------|------|

| File Ending | Description                            |  |

|-------------|----------------------------------------|--|

| _v7.lst     | Design files used with a Virtex-7 FPGA |  |

| _k7.lst     | Design files used with a Kintex-7 FPGA |  |

| _v6.lst     | Design files used with a Virtex-6 FPGA |  |

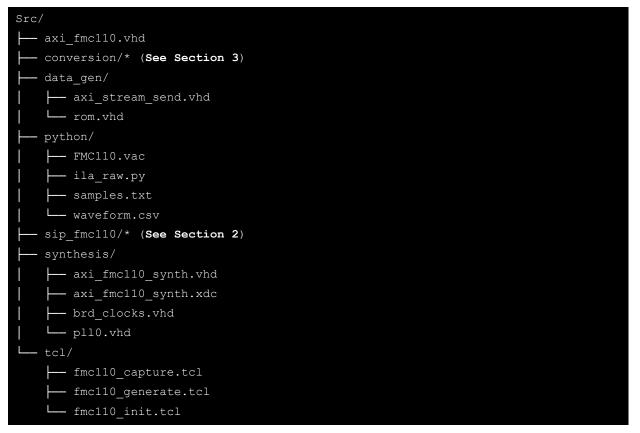

Since we are targeting a VC707 Carrier Board which has a Virtex-7 FPGA we look in the \*\_v7.lst file and copy each of the listed files in "/star\_lib/sip\_fmc110/sip\_files/sip\_fmc110\_v7.lst" to a local directory called "Src".

| Src/                     |

|--------------------------|

| L sip_fmc110             |

| ad9517_init_mem.ngc      |

| ad9517_init_mem.vhd      |

| ads5400_fifo.vhd         |

| ads5400_init_mem.ngc     |

| ads5400_init_mem.vhd     |

| ads5400_phy_fifo.ngc     |

| ads5400_phy_fifo.vhd     |

| ads5400_phy_sp_v7.vhd    |

| ads5400_storage_fifo.ngc |

| ads5400_storage_fifo.vhd |

|                          |

--- bit\_align\_machine.vhd

- --- dac5681z\_init\_mem.ngc

- --- dac5681z\_init\_mem.vhd

- dac5681z\_phy\_fifo.ngc

dac5681z\_phy\_fifo.vhd

- -- dac5681z\_phy\_v7.vhd

- -- dac5681z\_wfm\_ctrl.vhd

- -- dac5681z\_wfm\_dpram.ngc

- --- dac5681z\_wfm\_dpram.vhd

- --- dac5681z\_wfm\_input\_fifo.ngc

- --- dac5681z\_wfm\_input\_fifo.vhd

- --- dac5681z\_wfm\_output\_fifo.ngc

- --- dac5681z\_wfm\_output\_fifo.vhd

- --- dac5681z\_wfm.vhd

- --- dac\_mmcm.vhd

- dac\_mmcm.xco

- fmc110\_ad9517\_ctrl.vhd

- --- fmc110\_ads5400\_ctrl.vhd

- -- fmc110\_cpld\_ctrl.vhd

- fmc110\_ctrl.vhd

- fmc110\_dac5681z\_ctrl.vhd

- -- fmc110\_if\_v7.vhd

- fmc110\_stellar\_cmd.vhd

- pack\_16to12.vhd

- --- pulse2pulse.vhd

- --- serdes\_v7.vhd

- --- sip\_fmc110.vhd

- sip\_freq\_cnt16.vhd

# **3** Conversion entities

In the majority of cases StellarIP Blocks have just three types of interfaces: Data Wormhole Inputs (wh\_in), Data Wormhole Outputs (wh\_out) and StellarIP Commands (cmd\_in and cmd\_out). They will be converted into AXI4-Stream Slave, AXI4-Stream Master, and AXI4-Lite Slave interfaces respectively. Example entities to perform the interface conversion have been provided.

| Src/                      |  |

|---------------------------|--|

| L- conversion             |  |

| axistream_to_whin.vhd     |  |

| delay_bit.vhd             |  |

| stellarcmd_to_axilite.vhd |  |

| axis2wh_fifo.ngc          |  |

| axis2wh_fifo.vhd          |  |

| L- whout_to_axistream.vhd |  |

#### **Table 2: Conversion Entities**

| Conversion Entity         | From Interface    | To Interface       | Used For         |

|---------------------------|-------------------|--------------------|------------------|

| stellarcmd_to_axilite.vhd | StellarIP Command | AXI4-Lite Slave    | FMC1110 Commands |

| axistream_to_whin.vhd     | Wormhole Input    | AXI4-Stream Slave  | FMC110 DAC0/DAC1 |

| whout_to_axistream.vhd    | Wormhole Output   | AXI4-Stream Master | FMC110 ADC0/ADC1 |

### 3.1 Wormhole Output to AXI-Stream Master

A StellarIP output channel is typically made up of three signals: DATA, VALID and STOP. This works as expected: DATA contains the output data, VALID is HIGH when DATA holds valid data and STOP indicates that the receiver can no longer accept data and we should stop sending.

The conversion between a StellarIP output channel and an AXI-Stream Master is straight forward connection because the channels are mostly compatible. The only difficulty is that when a STOP is asserted in a StellarIP Interface data will not immediately stop flowing, it might take up-to 8 cycles, unlike with TREADY. To accommodate this we use a FWFT FIFO.

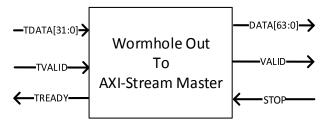

Figure 1: whout\_to\_axistream.vhd

All the signals in an AXI-Stream channel, except for ACLK, ARESETn and TVALID are optional. The other signals are set to their default values, see the AXI-Stream Standard for details.

### 3.2 Wormhole Input to AXI-Stream Slave

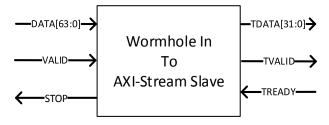

A StellarIP input channel is typically made up of three signals: DATA, VALID and STOP. This works as expected: the signal DATA contains the input data, the signal VALID is HIGH when the signal DATA holds valid data and the signal STOP provides back pressure when valid data can no longer be accepted.

The conversion between a StellarIP input channel and an AXI-Stream Slave is straight forward because the interfaces are compatible. In the AXI-Stream standard all signals expect for ACLK, ARESETn and TVALID are optional giving a straight forward conversion.

Figure 2: axistream\_to\_whin.vhd

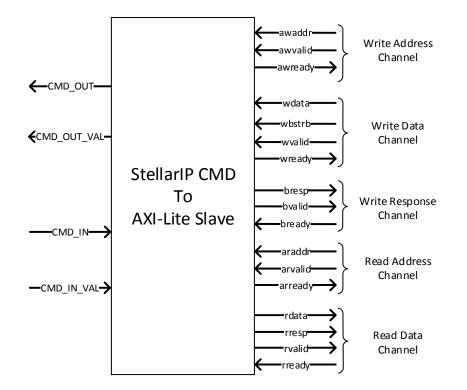

### 3.3 StellarIP Command to AXI-Lite

A StellarIP command interface is generally made of two signals: CMD and CMD\_VALID. The command signal is 64-bits wide.

| Table 3: Stella | Table 3: StellarIP Command Format |  |

|-----------------|-----------------------------------|--|

| Demas           | 62 60                             |  |

| Range       | 6360                     | 5932                    | 310                               |

|-------------|--------------------------|-------------------------|-----------------------------------|

| Field       | CMD                      | Address                 | Data                              |

| Description | The command defines      | Contains the address    | Contains the data we are going to |

|             | what is in the other     | which we are trying     | write when sent with CMD_WR.      |

|             | fields, it can be one of | to write to or read to. | Ignored when sent with CMD_RD.    |

|             | the following:           |                         | Contains the read data when       |

|             | $CMD_WR = 0b0001$        |                         | received with CMD_RD_ACK.         |

|             | CMD_RD = 0b0010          |                         |                                   |

|             | CMD_RD_ACK = 0b0100      |                         |                                   |

The interface is not bidirectional and require two pairs for writing and reading; CMD\_IN, CMD\_IN\_VALID, CMD\_OUT and CMD\_OUT\_VALID. The command interface can be thought as a distributed RAM with an address range which we read and write from. The conversion entity which has been provided, **stellarcmd\_to\_axilite.vhd**, is loosely based on the Xilinx AXI GPIO IP.

Figure 3: stellarcmd\_to\_axilite.vhd

The conversion is done by accepting a CMD\_IN StellarIP command and issuing an AXI-Lite command and also by accepting an AXI-Lite command and issuing a CMD\_OUT StellarIP command. The conversion can be best understood by becoming familiar with the AXI-Lite Standard. As an example, image a write of 0xAAAAAAAA to address 0x7. The address would come from the Write Address Channel and the data would come from the Write Data Channel. These would be combined to form the following StellarIP command:

#### 0x1 | 0x0000007 | 0xAAAAAAAA |

The command would be sent out CMD\_OUT and a reply would be sent through the Write Response Channel.

# **4** Wrapping into AXI

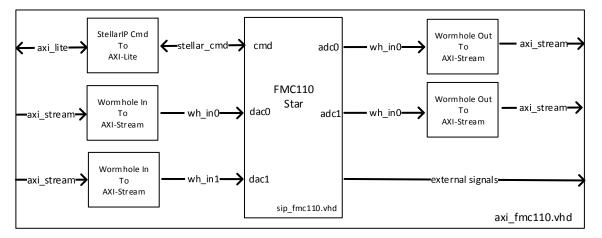

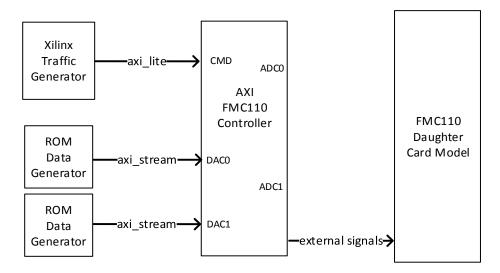

At this point we have the source code for the StellarIP Block we are going to reuse and the conversion entities that help speed up the process. Looking at top level entity, **sip\_fmc110.vhd**, for the FMC110 IP we can see that we have two wh\_in interfaces for each of the DACs, two wh\_out interfaces for each of the ADCs, and the command interface; cmd\_in and cmd\_out.

| 40 estitu cis (medd) ic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------|

| 63 entity sip_fmc110 is<br>64 generic (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                       |

| 65 GLOBAL START ADDR GEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e of d l | oqic vector(27 downto 0);                             |

| 66 GLOBAL_STOP_ADDR_GEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | ogic_vector(27 downto 0);                             |

| 67 PRIVATE START_ADDR_GEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | ogic_vector(27 downto 0);                             |

| 68 PRIVATE_STOP_ADDR_GEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | ogic_vector(27 downto 0),<br>ogic_vector(27 downto 0) |

| 68 PRIVATE_STOP_ADDR_GEN<br>69 );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . stu_1  | Ugic_veccor(27 downed 0)                              |

| 79 port (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                       |

| 78 port (<br>71Wormhole 'clk' of type 'clkin':                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                       |

| 72 clk clkin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | : in     | <pre>std logic vector(31 downto 0);</pre>             |

| 72 clk_clkin T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 10     | sta_rogic_vector(sr downed b);                        |

| 74Wormhole 'rst' of type 'rst_in':                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

| 75 rst rstin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | : in     | <pre>std logic vector(31 downto 0);</pre>             |

| 75 rst_rstin<br>76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | sed_rogic_veccor(or downed by;                        |

| 77 Wormhole 'emdelk in' of tune 'emdelk in'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                                       |

| 78 cmdclk in cmdclk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in       | std logic;                                            |

| <pre>77Wormhole 'cmdclk_in' of type 'cmdclk_in' 78  cmdclk_in_cmdclk 79</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | <u>-</u> <u>9</u> ,                                   |

| 80Wormhole 'cmd_in' of type 'cmd_in':<br>81 cmd_in_cmdin<br>82 cmd_in_cmdin_val<br>83                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                       |

| 81 cmd in cmdin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | : in     | <pre>std logic vector(63 downto 0);</pre>             |

| 82 cmd in cmdin val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | : in     | std logic;                                            |

| 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

| <pre>84Wormhole 'cmd_out' of type 'cmd_out':</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

| 85 cmd_out_cmdout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | : out    | <pre>std_logic_vector(63 downto 0);</pre>             |

| <pre>86 cmd_out_cmdout_val</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : out    | <pre>std_logic;</pre>                                 |

| 84Wormhole 'cmd_out' of type 'cmd_out':<br>85 cmd_out_cmdout<br>86 cmd_out_cmdout_val<br>87                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                                       |

| 88Wormhole 'adc0' of type 'wh_out':                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                       |

| <pre>89 adc0_out_stop</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | : in     | std_logic;                                            |

| 90 adc0_out_dval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : out    | <pre>std_logic;</pre>                                 |

| 91 adc0_out_data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : out    | <pre>std_logic_vector(63 downto 0);</pre>             |

| 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

| 98Wormhole 'adc1' of type 'wh_out':                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                       |

| 94 adc1_out_stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : in     | <pre>std_logic;</pre>                                 |

| 95 adc1_out_oval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : out    | <pre>std_logic;</pre>                                 |

| 90 auci_ouc_uaca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | : out    | <pre>std_logic_vector(63 downto 0);</pre>             |

| 97<br>09Weymbolo 'dae@' of tupo 'wb ip's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                                       |

| <pre>98worwhole date of type win_in . 00 date in ctop</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | : out    | std logic:                                            |

| aco_in_scop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | : in     | std_logic;                                            |

| 1 dougung data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | : in     | <pre>std_logic vector(63 downto 0);</pre>             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | sta_iogic_vector(03 downed b);                        |

| 18 Wormhole 'dac1' of tune 'wh in':                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                       |

| A dar1 in ston                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | : out    | std logic;                                            |

| st dact_in_scop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | in       | std logic;                                            |

| 66 dac1 in data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | in       | <pre>std logic vector(63 downto 0);</pre>             |

| 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

| <pre>88Wormhole 'adc0' of type 'wh_out': 89 adc0_out_stop 90 adc0_out_dval 91 adc0_out_dval 92 93Wormhole 'adc1' of type 'wh_out': 94 adc1_out_stop 95 adc1_out_dval 96 adc1_out_dval 97 98Wormhole 'dac0' of type 'wh_in': 99 dac0_in_stop 90 dac0_in_dval 81 dac0_in_dval 81 dac0_in_dval 82Wormhole 'dac1' of type 'wh_in': 94 dac1_in_stop 95 dac1_in_dval 96 dac1_in_dval 97 98Wormhole 'dac1' of type 'wh_in': 94 dac1_in_stop 95 dac1_in_dval 96 dac1_in_dval 97 98Wormhole 'ext_fmc110' of type 'ext_fmc11 99 fnc_to_cpld</pre> | 0':      |                                                       |

| <pre>\$9 fmc to cpld</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | <pre>std logic vector(3 downto 0);</pre>              |

| 10 front_io_fmc<br>11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | <pre>std_logic_vector(3 downto 0);</pre>              |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                       |

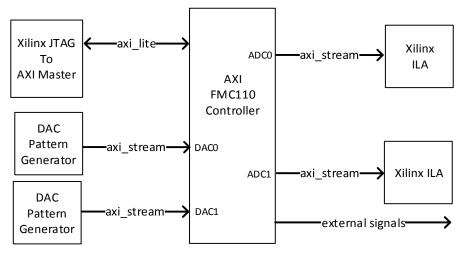

Each of these channels will be connected to the appropriate conversion entity. We create a new file, **axi\_fmc110.vhd**, that instantiates the StellarIP block we are reusing and one appropriate conversion entity for each of the interfaces. A block diagram of the final result is shown below.

Figure 4: Block Diagram of a StellarIP Block with AXI Interfaces

The external signals are simply propagated through the wrapper.

# **5** Simulate

It is a good idea to run a simulation to gain confidence that the design works.

## 5.1 File descriptions

For the simulation to work we need the following files.

#### Table 4: Simulation File Descriptions

| File or Folder | Description                                                                                                                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| axi_fmc110.vhd | This is the top level entity of the converted IP. We took an IP<br>Block from StellarIP and wrapped around conversion entities<br>to have an AXI Interface. This is explained in <b>Section 4</b> of this<br>document. |

| conversion/*   | This folder contains conversion entities provided as examples by 4DSP. These take typical StellarIP type of interfaces and                                                                                             |

|                                            | convert them to AVI interfaces. This was evaluated in Continue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | convert them to AXI Interfaces. This was explained in <b>Section</b><br><b>3</b> of this document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| sip_fmc110/*                               | This is the StellarIP Block source code we are reusing. This was explained in <b>Section 2</b> of this document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| simulation/axi_fmc110_tb.vhd               | This is the top level test bench, see the section below for creating this test bench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| data_gen/*                                 | This entity was created for this application note to function as<br>a simple AXI-Stream Master used to generate data that will<br>go into the DAC interface of the FMC110. When enabled it<br>sequentially reads a ROM and sends out the contents. It<br>produces a waveform that will be seen out of the DACs of the<br>FMC110 daughter card.                                                                                                                                                                                                                                         |

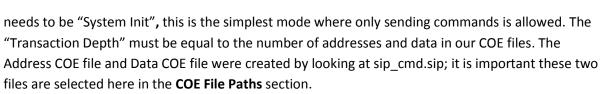

| simulation/addr.coe<br>simulation/data.coe | These files are used by the Xilinx Traffic Generator to<br>generate the write commands. StellarIP blocks work with<br>commands to configure the burst length, read status<br>information, enable capturing etc. Typically it is required to<br>read the documentation for the StellarIP block you are using<br>to figure what needs to be configured. Since an example is<br>provided, sip_cmd.sip, we can simply take the commands<br>from that file.                                                                                                                                 |

| simulation/sip_cmd.sip                     | Many StellarIP blocks come with simulation files including a file called sip_cmd.sip which contain a list of commands used by a StellarIP host interface model.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| simulation/ XilinxCoreLib/*                | In Vivado 2014.1 the XilinxCoreLib library has been removed.<br>This library contained simulation models for ISE IP cores such<br>as FIFOs and Block Memories. Simulation models of Xilinx<br>Vivado IP cores are delivered as an output product when the<br>IP is generated but because many StellarIP blocks have been<br>designed with ISE they depend on files from XilinxCoreLib for<br>simulation to work. We must copy the simulation files that<br>are being used from a previous version of ISE. A typical<br>location is "C:\Xilinx\14.7\ISE_DS\ISE\vhdl\src\XilinxCoreLib". |

| simulation/ fmc110_model/*                 | This is a simulation model for the FMC110 daughter card. It sends data through the external pins so we are able to simulate the capturing of the ADC data.                                                                                                                                                                                                                                                                                                                                                                                                                             |

www.4dsp.com

## 5.2 Creating the project

We will now step through creating the simulation project and running it.

1. Select Create New Project

- 2. Enter a project name and the location where to save it for **Project Name**.

- 3. Select RTL Project for Project Type

- 4. Click Next for Add Sources/ Add Constraints/ Add Existing IP

- 5. Select VC707 under Boards for Device Type

|   |                                                                                                    | New Projec                                                 | t              |                             |               |        |  |

|---|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------|-----------------------------|---------------|--------|--|

| e | Default Part<br>Choose a default Xilinx part or board for your project. This can be changed later. |                                                            |                |                             |               |        |  |

|   | Boards Display Nar                                                                                 | lor xilinx.com<br>ne All Remaining<br>ey Latest<br>Reset A |                | *<br>*<br>*                 |               |        |  |

|   | Display Name                                                                                       | Vendor                                                     | Board Rev      | Part                        | I/O Pin Count | File V |  |

|   | Artix-7 AC701 Evaluation Platform                                                                  | xilinx.com                                                 | 1.0            | xc7a200tfbg676-2            | 676           | 1.0    |  |

|   | Kintex-7 KC705 Evaluation Platform                                                                 |                                                            |                | xc7k325tffg900-2            | 900           | 1.0    |  |

|   | Virtex-7 VC707 Evaluation Platform                                                                 |                                                            |                | xc7vx485tffg1761-2          |               | 1.0    |  |

|   | Virtex-7 VC709 Evaluation Platform                                                                 | xilinx.com                                                 | 1.0            | xc7vx690tffg1761-2          |               | 1.0    |  |

|   | ZYNQ-7 ZC702 Evaluation Board                                                                      | xilinx.com                                                 | 1.0            | xc7z020clg484-1             | 484           | 1.0    |  |

|   | ZYNQ-7 ZC706 Evaluation Board                                                                      | xilinx.com                                                 | 1.1            | xc7z045ffg900-2             | 900           | 1.0    |  |

|   | <ul> <li>Infin</li> </ul>                                                                          |                                                            |                |                             |               | ¢      |  |

|   |                                                                                                    |                                                            | < <u>B</u> ack | <u>N</u> ext > <u>E</u> ini | sh Car        | ncel   |  |

6. Select Finish

At this point we have a Vivado project created and we now need to add all the design files. It is important to add files that are used for both synthesis and simulation by selecting **Add or Create Design Sources**. If the file is used only for simulation select **Add or Create Simulation Sources**.

7. Add the files from the conversion folder by selecting Add or Create Design Sources.

#### Add Sources

This guides you through the process of adding and creating sources for your project

Add or <u>C</u>reate Constraints

Add or Create Design Sources

Add or Create <u>S</u>imulation Sources

Add or Create DS<u>P</u> Sources

Add Existing <u>B</u>lock Design Sources

Add <u>E</u>xisting IP

- 8. Add the files from the sip\_fmc110 folder by selecting Add or Create Design Sources.

- 9. Add the file from the fmc110\_model folder by selecting Add or Create Simulation Sources.

- 10. Add the files from the data\_gen folder by selecting Add or Create Design Sources.

- 11. Add the files from the **XilinxCoreLib** folder by selecting **Add or Create Simulation Sources**. Make sure to change the library to **xilinxcorelib**.

| Add Sources                       |                                                                |                                |                        |                                           |                       |  |

|-----------------------------------|----------------------------------------------------------------|--------------------------------|------------------------|-------------------------------------------|-----------------------|--|

| Add or Cre                        | ate Simulation Sources                                         |                                |                        |                                           |                       |  |

|                                   | imulation specific HDL files, o<br>ind add it to your project. | r directories conta            | iining HDL files, to : | add to your project. Create a new         | source file           |  |

| Specify simu                      | ulation set: 🔓 sim_1                                           | •                              |                        |                                           |                       |  |

| Specify file :                    | set: 🛅 Design Sources 🔻                                        | ]                              |                        |                                           |                       |  |

| Index                             | Name                                                           | Library                        | Location               |                                           |                       |  |

| 1                                 | BLK_MEM_GEN_V6_1.vhd                                           |                                | 💌 /home/luis/          |                                           |                       |  |

| 2 🕲                               | BLK_MEM_GEN_V6_2.vhd                                           |                                | ✓ /home/luis/…         |                                           |                       |  |

| õ 3                               | ad9517_init_mem.mif                                            | N/A                            | /home/luis/            |                                           |                       |  |

| 50 4                              | ads5400_init_mem.mif                                           | N/A                            | /home/luis/            |                                           | $\left[\times\right]$ |  |

| s<br>5                            | dac5681z_init_mem.mif                                          | N/A                            | /home/luis/            |                                           |                       |  |

| 9 6<br>9 7                        | fifo_generator_v8_1.vhd<br>fifo_generator_v9_3.vhd             | xilinxcorelib<br>xilinxcorelib | /home/luis/            |                                           | <b>(*</b> )           |  |

|                                   |                                                                |                                |                        |                                           | 4                     |  |

|                                   | Add F                                                          | iles A                         | dd Directories         | <u>C</u> reate File                       |                       |  |

| Scan and                          | l add RTL include files into pr                                | oiect                          |                        |                                           |                       |  |

|                                   | rces into project                                              | ,<br>                          |                        |                                           |                       |  |

| I Add sources from subdirectories |                                                                |                                |                        |                                           |                       |  |

| 🗹 Include a                       | ll design s <u>o</u> urces for simulati                        | on                             |                        |                                           |                       |  |

|                                   |                                                                |                                |                        | < <u>B</u> ack <u>N</u> ext > <u>E</u> ir | nish Cancel           |  |

Next we will add the AXI Traffic Generator IP from the Xilinx IP Catalog. This is used to send configuration commands to our IP Block.

12. Open IP Catalog from Flow Navigator

13. Select AXI Traffic Generator

At this point we must configure the AXI Traffic Generator IP with the required settings. It is important we select "AXI4-Lite" as the protocol since this is the command interface we created for our IP. Mode

14. Select the appropriate settings

| Customize IP                                                                                                                                      |                                  |   |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---|--|--|--|--|

| AXI Traffic Generator (2.0)                                                                                                                       |                                  | 1 |  |  |  |  |

| 🍘 Documentation 늖 IP Location 🧔 Switch to Default                                                                                                 | S                                |   |  |  |  |  |

| M Show disabled ports<br>M_AXQ<br>M_AXQ_MASTER<br>M_AXQ_S_MASTER<br>M_AXQ_S_LAVE<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A | Component Name avi_traffic_gen_0 |   |  |  |  |  |

15. Select **OK**. This should synthesize the Traffic Generator IP.

## 5.3 Creating the test bench

We now create a new file, **axi\_fmc110\_tb.vhd**, by instantiating the blocks as shown below. An example on how to do this has been provided.

Figure 5: Block diagram of simulation top-level

### 5.4 Running Simulation

Once the top-level test bench is ready we can **Run Simulation.** Vivado will process the design files and a waveform viewer will appear.

#### 5.4.1 Command Interface

We first inspect that the appropriate commands are being sent from the Xilinx Traffic Generator Block through its AXI-Lite Interface. Add all the top level entity signals from the Xilinx Traffic Generator entity to the waveform viewer.

|                               |          |     |     |                      |        | 800.0 | 30 ns |       |      |       |      |         |          |        |       |       |           |          |          |

|-------------------------------|----------|-----|-----|----------------------|--------|-------|-------|-------|------|-------|------|---------|----------|--------|-------|-------|-----------|----------|----------|

| Name                          | Value    | 0 ņ | s   |                      | 500 ns |       | 1,000 | ns    | 11.5 | 00 ns | s    | 2,000 n | s        | 2, 500 | ns    | 3,000 | ) ns      | 3,500 ns | 4,000 ns |

| Traffic Gen                   |          |     |     |                      |        |       |       |       |      |       |      |         | <u> </u> |        |       |       |           |          |          |

| 😼 s_axi_aclk                  | 1        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 1 s_axi_aresetn               | 1        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 📲 m_axi_lite_ch1_awaddr(31:0) | 00002414 |     | 00  | . <mark>X</mark> 00. |        | . 00. | . 00  | X00.  | .)(0 | 0     | X 00 | 00      | X 00     | 00     | X     |       | (         | 0002404  |          |

| m_axi_lite_ch1_awprot(2:0)    | 0        |     |     |                      |        |       |       |       |      |       |      | Θ       |          |        |       |       |           |          |          |

| 🖫 m_axi_lite_ch1_awvalid      | 0        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       | · · · · · |          |          |

| ¼ m_axi_lite_ch1_awready      | 0        | 1   |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 📲 m_axi_lite_ch1_wdata[31:0]  | 0000008  |     | 000 | 000007               | 00     | 00008 | 00    | )(00. | .)(0 | 0     | X    | 0000000 | 98       | X 00   | . (00 | X     |           | 00000004 |          |

| 📲 m_axi_lite_ch1_wstrb(3:0)   | f        |     |     |                      |        |       |       |       |      |       |      | f       |          |        |       |       |           |          |          |

| 🎍 m_axi_lite_ch1_wvalid       | 0        |     |     |                      |        |       |       |       |      |       |      |         |          | ļ      |       |       | 1         |          |          |

| 🖫 m_axi_lite_ch1_wready       | 0        | L   |     |                      |        |       |       |       |      |       |      |         |          | L      |       |       | L         |          |          |

| 🛏 m_axi_lite_ch1_bresp[1:0]   | 0        | K   |     |                      |        |       |       |       |      |       |      | Θ       |          |        |       |       |           |          |          |

| 🖫 m_axi_lite_ch1_bvalid       | 1        | n   |     |                      |        |       |       |       |      |       |      |         |          | I      |       |       |           |          |          |

| 🆫 m_axi_lite_ch1_bready       | 1        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 📲 m_axi_lite_ch1_araddr(31:0) | 0000000  |     |     |                      |        |       |       |       |      |       |      | 000000  | 000      |        |       |       |           |          |          |

| 🚡 m_axi_lite_ch1_arvalid      | 0        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 🚡 m_axi_lite_ch1_arready      | 0        | L   |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 📲 m_axi_lite_ch1_rdata(31:0)  | 0000000  |     |     |                      |        |       |       |       |      |       |      | 000000  | 900      |        |       |       |           |          |          |

| ¼ m_axi_lite_ch1_rvalid       | 0        | n   |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| m_axi_lite_ch1_rresp[1:0]     | 0        |     |     |                      |        |       |       |       |      |       |      | 0       |          |        |       |       |           |          |          |

| ™ m_axi_lite_ch1_rready       | 0        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| 1 done                        | 0        |     |     |                      |        |       |       |       |      |       |      |         |          |        |       |       |           |          |          |

| •                             | 0000000  |     |     |                      |        |       |       |       | 0000 | 00000 |      |         |          |        |       |       | _X        | 00000035 | 5        |

Figure 6: Waveform view of the Traffic Generator

We can also confirm that commands are arriving in **fmc110\_ctrl.vhd**, for example the register NB\_BURSTS\_REG should get the value '1'. This demonstrates that conversion from AXI-Lite to StellarIP commands is working.

Once the Traffic Generator sends all its commands we should see DONE='1' and STATUS[1:0] = "01" indicated success.

#### 5.4.2 ADC and DAC Interfaces

For the ADC we should see ADC0\_TDATA with data when ADC0\_TVALID='1'. This data is generated in the FMC110 Model and captured by the FMC110 Controller.

For the DAC we should see data coming out on DAC0\_TDATA when DAC0\_VALID='1'. We can trace this data going to a memory entity inside the FMC110 IP Block. Once a trigger is sent, through the Traffic Generator, data is read out of the memory and seen on the external pins.

|      | axi_fmc110_tb_b                                          | ehav.wcfg* ×     |               |               |             |          |            |              | C          |

|------|----------------------------------------------------------|------------------|---------------|---------------|-------------|----------|------------|--------------|------------|

| ⇒    |                                                          |                  |               |               |             |          | 3.270000 u | S            |            |

| 8    | Name                                                     | Value            |               | 11 us         | 12 us       | 13 11    |            | 14 us        | 15 us      |

| 0+   |                                                          |                  |               | 1 us          |             |          |            | <u> </u>     |            |

| 0-   | •¥ s_axi_rresp[:<br>4 s_axi_rvalid                       |                  |               |               |             | ┢        | 9          |              |            |

| ٩    | us_axi_rvaild<br>us_axi_rready                           |                  |               |               |             | +        |            |              |            |

| \$5i | DAC0                                                     | °                |               |               |             |          |            |              |            |

|      |                                                          | 000000000000092  | 00000000      | 0000000       |             |          |            |              |            |

|      | • 📲 dac0 tkeep                                           |                  |               |               |             |          | f          |              |            |

|      | 🖫 dac0_tlast                                             | 0                |               |               |             |          |            |              |            |

| 12   |                                                          | 1                |               |               |             |          |            |              |            |

| 2    | - ddeo_courb                                             | 1                |               |               |             |          |            |              |            |

| ÷    | •¶dac0_tuser(                                            |                  |               |               |             | 000      | 0000       |              |            |

| Ę.   | 堝 dac0_tvalid                                            | 1                |               |               |             |          |            |              |            |

| ۰ľ   | ADC0                                                     |                  |               |               |             |          |            |              |            |

|      | • 📲 adc0_count                                           |                  |               |               | 0000        | -        |            |              | 0040       |

| Яl   | • dc0_tdata[                                             |                  |               | 0000000000000 | 0000        | -        |            | 011100       | 000fff0000 |

|      | ularia <mark>adc0_tvalid</mark><br>• <b>™</b> adc0_tkeep |                  |               |               |             |          |            |              |            |

| -    | adc0_tkeep<br>adc0_tlast                                 | 0                |               |               |             |          | 5          |              |            |

|      | ladc0_tready                                             |                  |               |               |             |          |            |              |            |

|      | ladc0_tstrb                                              | 0                |               |               |             |          |            |              |            |

|      | • 📲 adc0_tuser[                                          |                  |               |               |             | 000      | 00000      |              |            |

|      | • 📲 status[31:0]                                         | 00000035         |               | 00            | 000000      |          |            | 000000       | 35         |

|      | 😼 done                                                   | 1                |               |               |             |          |            |              |            |

|      | Debug                                                    |                  |               |               |             |          |            |              |            |

|      | 🚡 clk_cmd                                                | 1                |               |               |             |          |            |              |            |

|      | 崎 rst                                                    | 0                |               |               |             |          |            |              |            |

|      | 1 in_cmd_val                                             | 0                |               |               |             |          |            |              |            |

|      | •                                                        | 1000240400000004 | <u>. XXX.</u> | <u> XXXX</u>  | <u>XXXX</u> | <u>X</u> |            | 100024040000 | 0004       |

|      |                                                          |                  |               |               |             |          |            |              |            |

Figure 7: Waveform view of DAC0 and ADC0

We have successfully simulated the design. We were able to send commands to the StellarIP Block, we were able to capture data from the ADCs and we were able to play a waveform in the DACs.

# 6 Synthesize

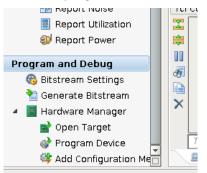

To have a synthesizable design we must make slight modifications to the simulation design. We switch the Xilinx Traffic Generator to Xilinx JTAG to AXI-Master. This gives us more control; it allows us to read as well as write and allows us to repeat a sequence of commands, for example, to capture ADC results multiple times. Also, we must capture the ADC data where we can view it; in simulation it is possible to add any signal to the waveform viewer. For synthesis we use the Xilinx Integrated Logic Analyser (ILA).

## 6.1 File Descriptions

The following files are used to synthesize the design and described below.

#### Table 5: Synthesis file descriptions

| File or Folder                 | Description                                                                                                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| synthesis/axi_fmc110_synth.vhd | Top level entity                                                                                                                       |

| synthesis/brd_clocks.vhd       | Clock generation entity. Accepts a differential external clock<br>and generate a 200 MHz and a 125 MHz clock using a PLL<br>(pll0.vhd) |

| synthesis/axi_fmc110_synth.xdc | Constraint file for VC707 + FMC110.                                                                                                    |

|                      | <b>Note:</b> When creating a constraint file it is important to know that everything is case sensitive, unlike VHDL. The signal names must match the case of the top level signal names. The Vivado commands need to be lower case, i.e., it is important to have set_property and not SET_PROPERTY.                                                                                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| python/ila_raw.py    | A script written in the Python programming language used to<br>read a CSV file, extract the data of interest, and convert the<br>data to the format required for processing. This is used on<br>python/waveform.csv which was generated with the Vivado<br>command <b>write_hw_ila_data.</b> The output of the Python<br>script is python/samples.txt which can be plotted and<br>analysed with VisualAnalog using the template python/<br>FMC110.vac. |

| python/FMC110.vac    | Design file for Analog Device's VisualAnalog Software, used to visualize and process data samples.                                                                                                                                                                                                                                                                                                                                                     |

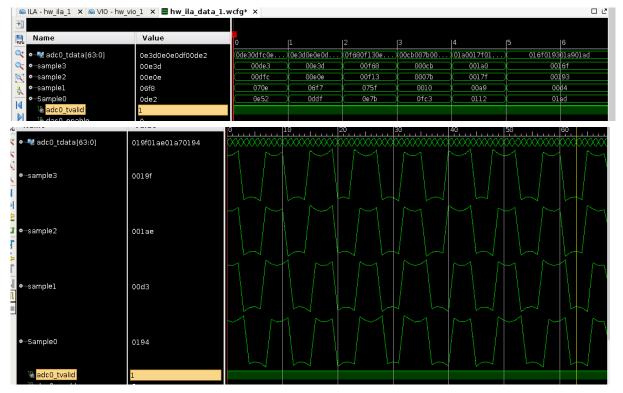

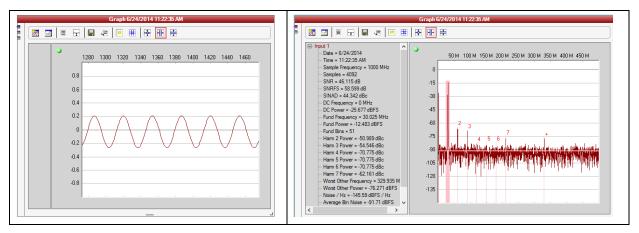

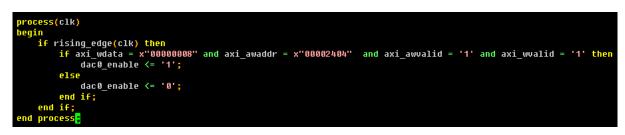

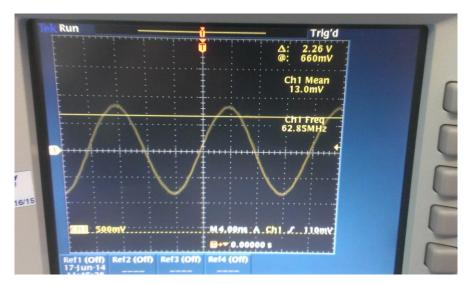

| tcl/ fmc110_init.tcl | Vivado TCL script to send commands through the Xilinx JTAG<br>to AXI Master IP. Used to initialize the FMC110 Card. More<br>information in the <b>Running Design</b> section.                                                                                                                                                                                                                                                                          |